# () synaptics

# DHX91 DHAN-S DECT ULE Module Datasheet

#### PN: 505-001250-01 Rev A

# 1. Description

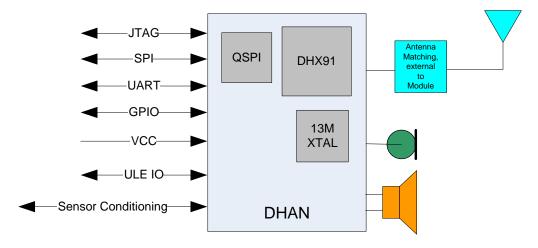

Synaptics' DHAN-S module is based on the state-of-theart DHX91, a 4th generation DECT System-on-Chip (SoC). The DHAN-S module is shipped with software that is immediately suited for a ULE device (node) where the application runs on an external MCU that communicates with the DHAN-S via the UART interface. In this configuration, the DHAN-S is simply a wireless transceiver. However, when loaded with the appropriate software stack, the DHAN-S module can also play other roles in the DECT ULE system: 1) Application Processor + wireless transceiver in a ULE device or GAP/CAT-IQ compliant cordless phone (CMHS),

2) communication transceiver in a ULE Hub or DECT Base Station (CMBS).

The DHAN-S features a compact mechanical footprint, hibernation mode which facilitates long battery life in IoT applications and excellent RF Link and Selectivity characteristics.

### 1.1. Features

- Excellent radio performance, with over 123 dB system gain

- Radio covers all regional DECT bands with a simple re-configuration of the EEPROM

- Fully compliant with ETSI, FCC DECT and ULE standards

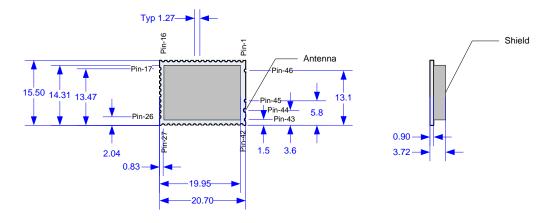

- Compact footprint: 20.7 x 15.5 x 3.72 mm (including the RF shield height)

- Hibernation mode current of < 2µA extends battery life to >5 years for many IoT applications

- Operating temperature: -20°C to 70°C

### 1.2. Block Diagram

Figure 1. DHX91 DHAN-S Module Block Diagram

# Contents

| 1.  | Descri<br>1.1.                                                         | iption<br>Features                                                                                                                             |                  |

|-----|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|     | 1.2.                                                                   | Block Diagram                                                                                                                                  | 2                |

| 2.  | Pin an                                                                 | nd Signal Description                                                                                                                          | 4                |

| 3.  | Electri<br>3.1.<br>3.2.<br>3.3.<br>3.4.<br>3.5.                        | ical Specifications<br>Absolute Maximum Rating<br>Recommended Operating Conditions<br>Peak and Hibernation Currents<br>Transmitter<br>Receiver | 7<br>7<br>8<br>8 |

| 4.  | Softwa                                                                 | are Image and Customization1                                                                                                                   | 0                |

| 5.  | Applic<br>5.1.<br>5.2.<br>5.3.<br>5.4.<br>5.5.<br>5.6.<br>5.7.<br>5.8. | ation Reference Schematic                                                                                                                      | 122222           |

| 6.  | Stand                                                                  | alone Applications1                                                                                                                            | 4                |

| 7.  | Applic<br>7.1.                                                         | ation PCB Design Recommendations                                                                                                               | 5<br>5<br>5      |

| 8.  | Assem<br>8.1.<br>8.2.<br>8.3.<br>8.4.<br>8.5.                          | hbly Information                                                                                                                               | .7<br>.8<br>.9   |

| 9.  | Supple<br>9.1.<br>9.2.<br>9.3.<br>9.4.<br>9.5.                         | ementary Information                                                                                                                           | 1<br>1<br>1      |

| 10. | Revisi                                                                 | on History2                                                                                                                                    | 3                |

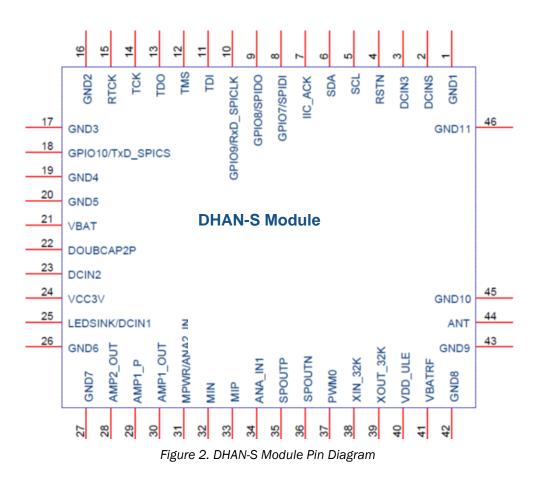

# 2. Pin and Signal Description

See Figure 2 and Table 2 for detailed pin diagram and description.

Table 1. DHAN-S Module Pin Description

| Pin No. | Name            | Description/Type                                                                                                                                                               |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND             | GND                                                                                                                                                                            |

| 2       | DCINS           | Leave not connected (NC)                                                                                                                                                       |

| 3       | DCIN3           | ADC input used to monitor battery level. Input level should be <3.2V. See Application Schematic section below                                                                  |

| 4       | RSTN            | For systems using an external application MCU, this pin can be connected to an MCU Output and used to reset the DHAN-S – See Application Schematic section (5) for more detail |

| 5       | SCL (GPIOO)     | GPIO or I2C Clock. Open Drain, reset value is floating. Leave NC if not used. See Note 1 $$                                                                                    |

| 6       | SDA (GPIO1)     | GPIO or I2C Data. Open Drain, reset value is floating. Leave NC if not used. See Note 1 $\ensuremath{1}$                                                                       |

| 7       | IIC_ACK (GPI03) | GPIO or I2C ACK. Leave NC if not used                                                                                                                                          |

| 8       | GPIO7           | GPIO or SPI Data In. Leave NC if not used. See Note 1                                                                                                                          |

| 9       | GPI08           | GPIO or SPI Data Out. Leave NC if not used. See Note 1                                                                                                                         |

Copyright © 2016 – 2022 Synaptics Incorporated. All Rights Reserved.

Synaptics Confidential. Disclosed Only Under NDA.

| Pin No. | Name         | Description/Type                                                                                                                                                                                                                              |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | RxD (GPIO9)  | GPIO or UART Rx (most typically) or SPICLK. See Note 1                                                                                                                                                                                        |

| 11      | TDI          | JTAG Data In. Should be connected to TP (see Application Schematic section (5) for more detail)                                                                                                                                               |

| 12      | TMS          | JTAG Mode Select. Connect to TP                                                                                                                                                                                                               |

| 13      | TDO          | JTAG Data Out. Connect to TP                                                                                                                                                                                                                  |

| 14      | тск          | JTAG Clock. Connect to TP                                                                                                                                                                                                                     |

| 15      | RTCK         | JTAG Reset. Connect to TP                                                                                                                                                                                                                     |

| 16-17   | GND          | GND                                                                                                                                                                                                                                           |

| 18      | TxD (GPI010) | GPIO or UART Tx or SPICS. See Note 1                                                                                                                                                                                                          |

| 19      | GND          |                                                                                                                                                                                                                                               |

| 20      | GND          |                                                                                                                                                                                                                                               |

| 21      | VCC          | Power Supply Input. Connect to battery or regulated supply                                                                                                                                                                                    |

| 22      | DOUBCAP2P    | Pull down with 1M if VCC $\ge$ 3.1V                                                                                                                                                                                                           |

| 23      | DCIN2        | Leave NC                                                                                                                                                                                                                                      |

| 24      | VCC3V        | 3V (Doubler) <b>Output</b> . While DHAN-S is hibernating, this pin is either in tristate (default SW configuration) or pulled to GND. Can be used in conjunction with GPI07 and 8 above to drive a LED or button during non-hibernation modes |

| 25      | LEDSINK/DCIN | ULE I/O. Leave NC when VCC $\ge$ 3.3V                                                                                                                                                                                                         |

| 26-27   | GND          | GND                                                                                                                                                                                                                                           |

| 28      | AMP2_OUT     | ULE I/O. Leave NC if not used.                                                                                                                                                                                                                |

| 29      | AMP1_P       | ULE non-inverting sensor conditioning input                                                                                                                                                                                                   |

| 30      | AMP1_OUT     | ULE I/O. Leave NC if not used.                                                                                                                                                                                                                |

| 31      | MPWR/ANA2_IN | ULE I/O (or Microphone Power). During hibernate, Logic High should not be applied to this pin (it can result in leakage current). If not used, can be left NC                                                                                 |

| 32      | MIN          | Leave NC if not used.                                                                                                                                                                                                                         |

| 33      | MIP          | Leave NC if not used.                                                                                                                                                                                                                         |

| 34      | ANA_IN1      | ULE I/O. Leave NC if not used.                                                                                                                                                                                                                |

| 35      | SPOUTP       | Leave NC if not used.                                                                                                                                                                                                                         |

| 36      | SPOUTN       | Leave NC if not used.                                                                                                                                                                                                                         |

| 37      | PWMO         | Analog Output                                                                                                                                                                                                                                 |

| 38      | XIN_32K      |                                                                                                                                                                                                                                               |

| 39      | XOUT_32K     |                                                                                                                                                                                                                                               |

| 40      | VDD_ULE      | 1.8V test point. Active during hibernate. Leave NC                                                                                                                                                                                            |

| 41      | VccRF        | Power Supply Input to RF. Add 10 pF bypass capacitor adjacent to this pin!                                                                                                                                                                    |

| 42-43   | GND          | GND                                                                                                                                                                                                                                           |

| 44      | Antenna      | RF In/Out, 50 Ohm                                                                                                                                                                                                                             |

Synaptics Confidential. Disclosed Only Under NDA.

| Pin No. | Name | Description/Type |

|---------|------|------------------|

| 45-46   | GND  | GND              |

**Note:** GPIOs 0, 1, 7, 3, 8 and 9 are not powered during hibernation. Furthermore, these pins are not back-drive protected. Therefore, do NOT to apply voltage to these pins during hibernation, as this voltage will likely leak to the I/O supply rails and result in undesirable leakage current. Additionally, when entering or exiting hibernation, these GPIOs will experience a 10mS positive-going pulse.

# 3. Electrical Specifications

All parameters are for 25°C.

### 3.1. Absolute Maximum Rating

Table 2. Absolute Maximum Rating

| Pin Name            | Pin                | Min  | Max | Unit |

|---------------------|--------------------|------|-----|------|

| VCC                 | 21                 | -0.3 | 4.6 | V    |

| VccRF               | 41                 | -0.3 | 4.6 | V    |

| 120                 | 5, 6, 7            | -0.3 | 4.6 | V    |

| JTAG                | 11, 12, 13, 14, 15 | -0.3 | 4.6 | V    |

| GPIO                | 8, 9, 10, 18       | -0.3 | 4.6 | V    |

| DCINs,DCIN1,2,3     | 2, 3, 23, 25       | -0.3 | 4.6 | V    |

| Storage Temperature | -                  | -45  | +90 | °C   |

**Note:** Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### 3.2. Recommended Operating Conditions

Table 3. Recommended Operating Conditions

| Rating                        | Conditions                                            | Min        | Тур | Max        | Unit |

|-------------------------------|-------------------------------------------------------|------------|-----|------------|------|

| Operating ambient temperature |                                                       | -20*       | +25 | +70        | °C   |

| VccRF, VCC                    |                                                       | 1.95       | 3.0 | 3.6        | V    |

| JTAG, UART                    | VIL<br>VIH<br>VOL<br>VOH<br>(VCC is at<br>nominal 3V) | 2.0<br>2.4 |     | 0.8<br>0.4 | V    |

| DCIN3                         |                                                       | 1.95       | 3.0 | VCC        | V    |

Note: Part # DHX91MDMCFBH6AMI can operate down to -40°C.

### 3.3. Peak and Hibernation Currents

Table 4. Peak and Hibernation Currents

| Parameter   | Test Conditions                          | Тур | Max | Unit |

|-------------|------------------------------------------|-----|-----|------|

| Tx Current  | VccRF=3 V<br>VCC=3 V<br>Band=EU @ 23dBm  | 400 | 480 | mA   |

| Tx Current  | VccRF=3 V<br>VCC=3 V<br>Band=US @ 21 dBm | 250 | 300 | mA   |

| Rx Current  | VccRF=3 V<br>VCC=3 V                     | 125 | 135 | mA   |

| Hibernation | VccRF=3 V<br>VCC=3 V                     | 1.7 | 2.5 | μA   |

### 3.4. Transmitter

Table 5. Tx Characteristics

| Characteristics         | Test Conditions                                             | Min  | Тур                      | Max                     | Unit     |

|-------------------------|-------------------------------------------------------------|------|--------------------------|-------------------------|----------|

| NTP                     | VccRF=3 V<br>VCC=3 V<br>Band=EU                             | 21.5 | 23                       | 24                      | dBm      |

| NTP                     | VccRF=3 V<br>VCC=3 V<br>Band=US                             | 19   | 20                       | 21                      | dBm      |

| Harmonics               | VccRF=3 V<br>VCC=3 V<br>Band=EU & US                        |      | -40                      | -35                     | dBm      |

| Transmission Mask       | EN 301406<br>Paragraph 5.3.3                                |      | Comply                   |                         | N/A      |

| Frequency Offset        | EN 301406<br>Paragraph 5.3.1                                | -50  | 8                        | +50                     | KHz      |

| Frequency Drift         | EN 301406<br>Paragraph 5.3.5                                | -15  | 0                        | +15                     | KHz/Slot |

| Emission Due Modulation | EN 301406<br>Paragraph 5.3.6.2<br>M±1<br>M±2<br>M±3<br>M>±3 |      | -20<br>-42<br>-47<br>-50 | -8<br>-30<br>-40<br>-44 | dBm      |

### 3.5. Receiver

Table 6. Rx Characteristics

| Characteristics               | Test Conditions      | Min | Тур | Max | Unit |

|-------------------------------|----------------------|-----|-----|-----|------|

| Sensitivity, BER <<br>1000ppm | VccRF=3 V<br>VCC=3 V |     | -96 | -93 | dBm  |

| Maximum input power           | VccRF=3 V<br>VCC=3 V |     |     | 15  | dBm  |

# 4. Software Image and Customization

There are two different methods for loading a new SW image or modifying EEPROM parameters on the DHAN-S:

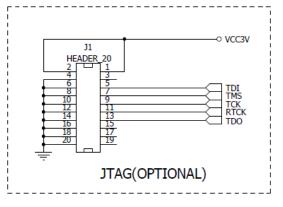

- Via JTAG (see following section for schematic implications) using a JTAG Adaptor Board (USB-UAJTI2C-CNV.BRD)

- Via UART I/F using CMND API features Multiple modules can be flashed in parallel using this interface

During the development cycle, it is convenient to have access to the JTAG I/F. Therefore, customers are encouraged to include this connector on their application PCB layout – see the following section for schematic recommendation. For the production line, if customers need to burn a new image on their DHAN-S (for example, DHAN-S runs the application, DHAN-S is the ULE Controller, standard SDK does not supply needed functionality), the UART I/F should be available as a connector or as Test Points to facilitate fixturing and programming in parallel multiple modules – See Reference "ULE Device Production Flow with DHAN-S".

The DHAN-S module is loaded with the standard HAN-FUN SDK image, configured for application control by an external MCU via the UART CMND API – see HAN FUN - CMND API SPEC. If the customer application runs on an external MCU and the DHAN-S is required for wireless connectivity only, in most cases the customer will not need to burn a new SW image. However, certain EEPROM Parameters WILL require updating. During the development cycle this can be accomplished by either JTAG or UART I/F. In production, the Host MCU can use the CMND API Production and Parameter Tools to initialize the relevant EEPROM settings at power up or reset.

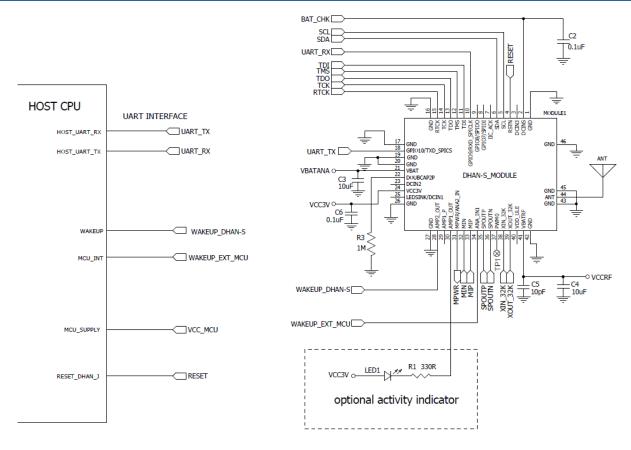

# 5. Application Reference Schematic

Figure 3. DHAN-S Reference Schematic

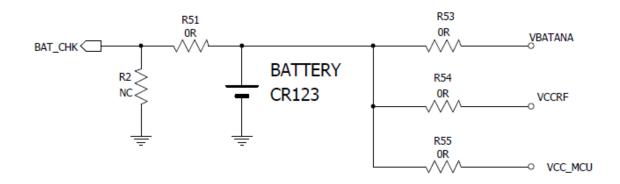

#### 5.1. Power Supply Detail

Figure 4. Power Supply

### 5.2. JTAG Connection

#### Figure 5. JTAG

Easy access to the JTAG interface is a MUST for customers requiring a SW image other than the ULE, Dual-mode SDK stack which is standard on the DHAN-S. The standard 20-pin connector shown in the reference schematic is convenient if the application board can accommodate it. Alternatively, test pins should be added which can be accessed during both prototyping and production.

#### 5.3. RSTN Input

At power-up, the Application Host on the external MCU should hold this pin at logic Low until it is ready to establish communication (via UART) with the DHAN-S. When ready, the Application Host should apply a rising edge (and leave at Logic High) and wait for the "Hello" indication from the DHAN-S. If at some point later on the MCU cannot communicate with the DHAN-S, it should apply a low going pulse of >100  $\mu$ S to reset the DHX91 on the DHAN-S.

### 5.4. Wake Up Input

Wake up the DHAN-S (from hibernation) by applying a positive-going edge to AMP2\_OUT (pin 27). The DHAN-S will reply at the (UART) CMND API with a "Hello\_Ind". The wakeup signal can then be lowered.

### 5.5. Wake Up Output

In applications where the device can be paged by the Hub, the external MCU can enter hibernation. When paged, the DHAN-S informs the external MCU via UART. If needed, the DHAN-S can wake up the external MCU by applying a rising edge from ANA\_IN1 (pin 33).

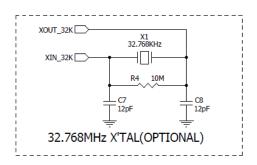

### 5.6. 32KHz XTAL

Figure 6. 32 KHz XTAL

Many battery-powered applications can leverage the DHX91 (on-board) 32.768 KHz RC oscillator to maintain a clock during hibernation and therefore the XIN/OUT\_32K pins can be left unconnected. Similarly, AC-powered devices that do not hibernate can also omit this XTAL. However, customer applications that require the radio to wake up at short (<60s) intervals to check for an incoming page from the ULE controller ("pageable") will require this XTAL.

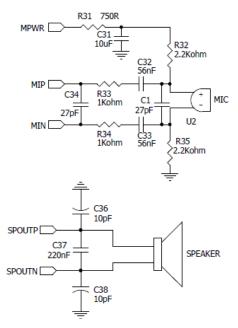

#### 5.7. Microphone and Speaker

Dual-mode applications (or CMHS applications) can make use of the microphone and speaker, as shown in Figure 7.

Figure 7. Microphone and Speaker

#### 5.8. Other Notes

- For standalone DHAN-S applications, the external MCU can be removed.

- For alkaline batteries (AAA or AA) or CR2 battery, a bulk cap of 100μF should be applied close to Vcc RF (C4 shown in schematic). For CR123 battery, C4 of 10μF as shown is suitable.

- The 20-pin JTAG connector is optional. It is recommended for those developing applications on the DHAN-S (DHX91) where debug and reprogramming of the SW image is a must. For applications running on an external MCU, the image on the DHAN-S as shipped should suffice.

- Audio interface is required for dual-mode ULE applications only.

- Sensor interface (I2C or otherwise) is relevant when the Application Host runs on the DHAN-S. When the Application Host runs on an external MCU, sensors or actuators should interface with it and DHAN-S should be used for wireless connectivity only.

- The 32KHz XTAL is required for ULE devices that must respond to incoming paging from the Hub with lowlatency (within seconds or tens of seconds).

# 6. Standalone Applications

The DHX91 ULE block includes a Sensor Conditioning Module that can facilitate many types of ULE applications. This module is a highly configurable analog circuit that can be used to interface to a wide variety of sensor transducers.

The module is built around the following sub-circuits:

- Two analog operational amplifiers (op-Amps) with shared bias source

- Two analog comparators with digital output

- One configurable digital potentiometer

- Three configurable ratiometric voltage references with selectable source

- Several analog distribution MUXes

- Several sample-and-hold (S&H) mechanisms

For more information about the Sensor Conditioning Module, please contact your Synaptics representative.

# 7. Application PCB Design Recommendations

It is recommended that unused pads on the Application PCB not be left as isolated islands of copper but rather be anchored with via to inner layers of the PCB. It is also recommended that GND vias be applied liberally in the vicinity of the antenna pin (44) and the associated GND pins (43, 45, 46).

The following layout recommendations need to be applied on the Main Board:

- 1. Implement a solid ground under the DHAN-S module.

- 2. Do not route signal traces under the module. Use the bottom layer for signal routing.

- 3. Make sure no components are near the antenna.

- 4. Locate the antenna on the edge of the PCB.

- 5. Use coplanar wave-guide trace between the DHAN-S module and antenna. It should be designed to be as short as possible with  $50\Omega$  impedance.

- 6. Add GND vias alongside the RF trace.

- 7. Route the RF trace with gradual bends and no sharp corners.

- 8. Design the antenna position according to the common usage/position of the ULE product for optimal range.

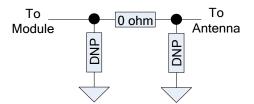

#### 7.1. Antenna Recommendations

A Pi-scheme should be added between the DHAN-S module antenna port and the antenna. This circuit will be used for antenna matching, if needed.

Figure 8. Pi-Scheme for Antenna Matching

Applications can use chip, wire or printed antennas, the latter being the most cost-effective and assembly- friendly. However, it requires space on the application PCB.

#### 7.1.1. Wire Antennas

The wire antenna should be bent according to the cabinet structure one should try to implement minimal of parallel structures. The total length of the wire antenna should be ¼ Lambda (~40.0 mm). It is important to ensure an adequate ground plane near the antenna port in order to obtain maximal antenna gain and efficiency.

#### 7.1.2. Chip Antennas

| P/N               | Manufacturer |

|-------------------|--------------|

| H2U74W1H1M0100    | Unictron     |

| ANT8868LL00R1880A | Yageo        |

| CAN4311112001881K | Yageo        |

| W3022             | Pulse Elect  |

#### 7.1.3. Printed Antennas

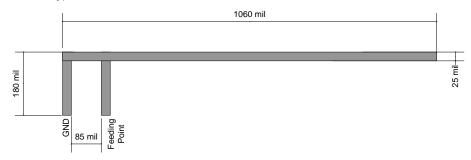

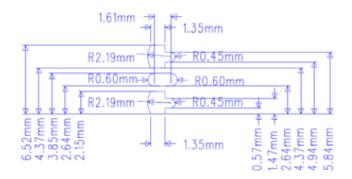

The most popular printed antennas are INV-F-Antenna and monopole antenna. RF CAD tools are recommended to use for design. Figure 9 shows typical INV-F-Antenna dimensions for DECT band.

Figure 9. INV-F-Antenna Dimensions

A practical, more compact version of this inverted-F is shown below. Contact DSP Group to obtain the design file.

Figure 10. INV-F-Antenna Compact Version

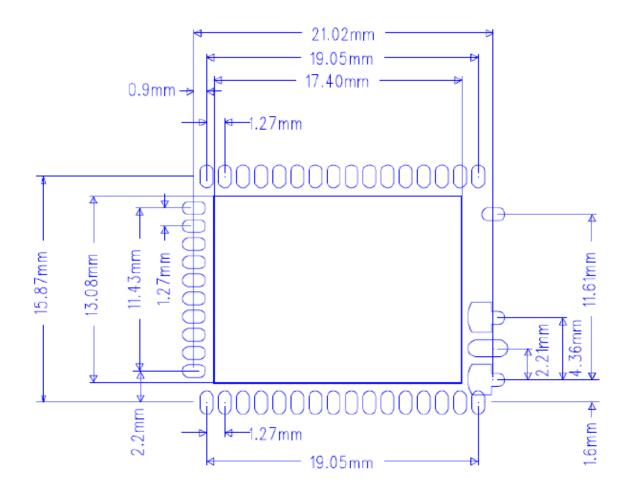

# 8. Assembly Information

Electronic version of the information in this section is available.

### 8.1. Mechanical Drawing

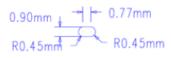

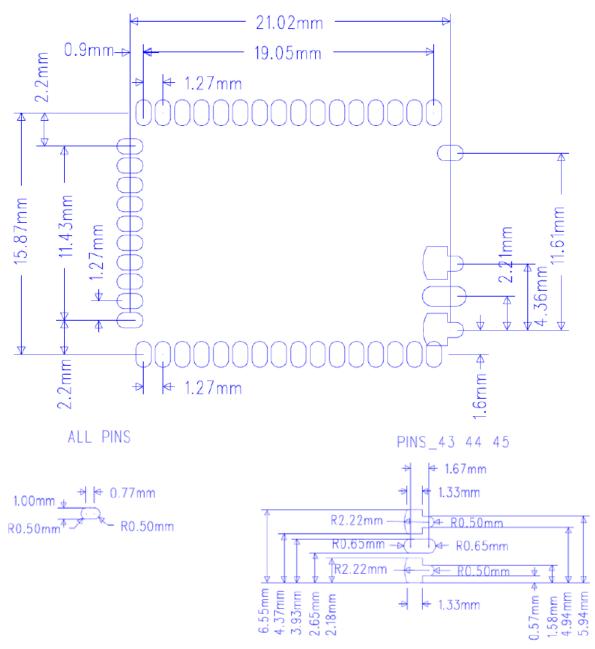

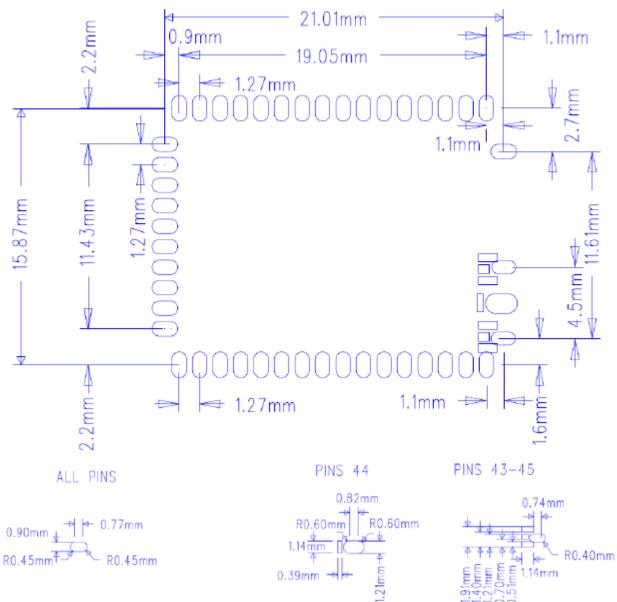

### 8.2. PCB Metal Land Pattern Recommendation

ALL PINS

PINS 43 44 45

### 8.3. PCB Solder Mask Recommendation

### 8.5. Pick & Place, Reflow

The DHAN-S module uses a flat shield cover to facilitate a fully automatic assembly process. For backing and reflow recommendations, use MSL 3 in the JEDEC/IPC standard J-STD-20b. The temperature classification (TC) for the module is 245 °C.

# 9. Supplementary Information

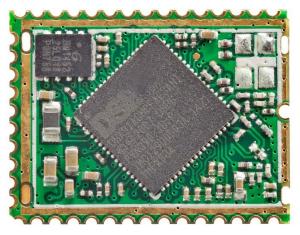

### 9.1. DHAN-S Module Photo

Figure 11. DHAN-S Module

### 9.2. Labeling

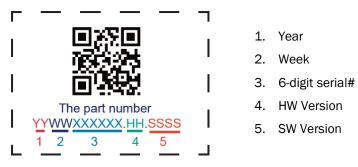

See Figure 12 for labeling details. The label is attached to the module shield.

Figure 12. DHAN-S Module Labeling Details

### 9.3. FCC ID, Industry Canada, ETSI and JDECT

While the DHAN-S has been tested for compliance with these regulatory standards, it currently has not been certified by any test house. See Reference 3 for detailed guidance on conducting FCC certification for a ULE device.

### 9.4. IPEI and EMC

Each DHAN-S module is shipped to the customer with a unique IPEI. The IPEI is the ULE device's unique identity. The IPEI is stored in the DECT portion of the EEPROM. The DHAN-S IPEI is hexadecimal 2E9Exxxxx, where xxxxx ranges from 0x00600 to 0xFFFFF. The IPEI is the modules unique identifier.

The DHAN-S will ship with an "EMC" of 0xFEB. This is DSP Group's "generic" EMC. The EMC setting identifies a Device as belonging to a specific group of ULE Devices/Hubs that utilize some proprietary signaling.

In either case, the customer is free to re-program these parameters.

## 9.5. Ordering Information

| Part NO.                  | SW Image                              |

|---------------------------|---------------------------------------|

| DHX91MDMCFB <b>G</b> 6AMI | T_HAN_DEVICE_1.1.K_32.28_19DEC2017    |

| DHX91MDMCFB <b>H</b> 6AMI | T_HAN_DEVICE_1.1.K_32.28.01_05JUL2019 |

# **10. Revision History**

| Revision | Description               |

|----------|---------------------------|

| А        | Initial Synaptics release |

# Copyright

Copyright © 2016 - 2022 Synaptics Incorporated. All Rights Reserved.

## Trademarks

Synaptics and the Synaptics logo, are trademarks or registered trademarks of Synaptics Incorporated in the United States and/or other countries.

All other trademarks are the properties of their respective owners.

# Notice

This document contains information that is proprietary to Synaptics Incorporated ("Synaptics"). The holder of this document shall treat all information contained herein as confidential, shall use the information only for its intended purpose, and shall not duplicate, disclose, or disseminate any of this information in any manner unless Synaptics has otherwise provided express, written permission.

Use of the materials may require a license of intellectual property from a third party or from Synaptics. This document conveys no express or implied licenses to any intellectual property rights belonging to Synaptics or any other party. Synaptics may, from time to time and at its sole option, update the information contained in this document without notice.

INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED "AS-IS," AND SYNAPTICS HEREBY DISCLAIMS ALL EXPRESS OR IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND ANY WARRANTIES OF NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT SHALL SYNAPTICS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES ARISING OUT OF OR IN CONNECTION WITH THE USE OF THE INFORMATION CONTAINED IN THIS DOCUMENT, HOWEVER CAUSED AND BASED ON ANY THEORY OF LIABILITY, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, AND EVEN IF SYNAPTICS WAS ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. IF A TRIBUNAL OF COMPETENT JURISDICTION DOES NOT PERMIT THE DISCLAIMER OF DIRECT DAMAGES OR ANY OTHER DAMAGES, SYNAPTICS' TOTAL CUMULATIVE LIABILITY TO ANY PARTY SHALL NOT EXCEED ONE HUNDRED U.S. DOLLARS.

# Contact Us

Visit our website at www.synaptics.com to locate the Synaptics office nearest you.